## SIN1 Additionneur

## Etude d'un additionneur

L'algorithme de l'addition en binaire est le même qu'en décimal.

En décimal :

Exemple: la somme 5 + 7 = 12, Chiffre des unités = résultat = 2 Chiffre des dizaines = retenue = 1 et vient s'ajouter aux chiffre de rang immédiatement supérieur

On commence par faire la somme entre les chiffres des unités (poids faibles en binaire).

Si il existe un symbole de la base dont la valeur est égale à cette somme, il correspond au chiffre du résultat (ex: 4+3=7)

Si la somme est strictement supérieure à 9, ( elle restera forcément inférieure ou égale à 19 ), alors le chiffre résultat correspond à l'unité de cette somme et le chiffre des dizaine

(forcement égal à 1) vient s'ajouter aux chiffres de rang immédiatement supérieur et s'appelle « retenue ».

En binaire le principe est le même :

En binaire:

1101

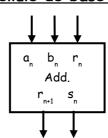

Cellule de base :

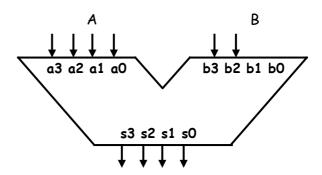

Un additionneur, n bits, peut être réalisé en cascadant n cellules de base. Chaque cellule génère le bit résultat «  $s_n$  » et le bit retenue «  $r_{n+1}$  », à partir des trois bits d'entrée :

- $\mathbf{a}_n$  (bit de rang n du nombre A)

- $b_n$  (bit de rang n du nombre B)

- $\mathbf{r}_{\mathsf{n}}$  (retenue générée par la cellule de rang n-1)

- Etablir le schéma interne de la cellule de base d'un additionneur 1/ Pour cela réaliser les étapes suivantes :

- écrire la table de vérité de la cellule de base a/

- b/ en déduire pour chaque sortie une équation non simplifiée

- simplifier chaque équation en utilisant les propriétés des c/ opérateurs logiques

- d/ remplir des tableaux de Karnaugh pour chaque sortie

- en extraire directement les équations simplifiées e/

- f/ faire le schéma de la cellule de base

## SIN1 TD Additionneur

- 2/ Ecrire la description VHDL de la cellule de base en n'utilisant que des affectations simples

- 3/ Ecrire la description VHDL de la cellule de base en utilisant : une affectation conditionnelle « when ... else ... » pour le bit de somme et une affectation sélective « with ... select ... » pour le bit de retenue.

- 4/ Ecrire la description VHDL de la cellule de base en n'utilisant qu'une seule affectation (conditionnelle ou sélective).

- 5/ Etablir le schéma d'un additionneur 4 bits à l'aide de 4 cellules de base en cascade.